## **Do Not Copy**

## DESCRIPTION

The Signetice 25000 Series 9946XN Random Access Write-Only-Memory employs both enhancement and depletion mode P-Channel, N-Channel, and neu(1) channel MOS devices. Although a static device, a single TTL level clock phase is required to drive the on-board multi-port clock generator. Data refresh is accomplished during CB and LH periods<sup>(11)</sup>. Quadri-state outputs (when applicable) allow expansion in many directions, depending on organization.

The static memory cells are operated dynamically to yield extremely low power dissipation. All inputs and outputs are directly TTL compatible when proper interfacing circuitry is employed.

Device construction is more or less S.O.S.(2).

#### **FEATURES**

- FULLY ENCODED MULTI-PORT ADDRESSING

- WRITE CYCLE TIME 80nS (MAX. TYPICAL)

- WRITE ACCESS TIME(3)

- POWER DISSIPATION 10uW/BIT TYPICAL

- CELL REFRESH TIME 2mS (MIN. TYPICAL)

- TTL/DTL COMPATIBLE INPUTS(4)

- AVAILABLE OUTPUTS "n"

- CLOCK LINE CAPACITANCE 2pf MAX. (5)

- V<sub>CC</sub> = +10V

- $V_{DD} = OV \pm 2\%$

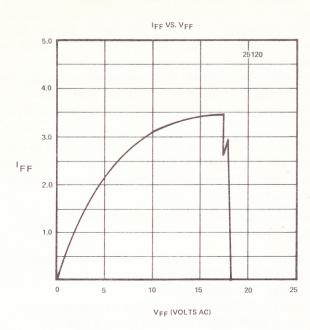

- $V_{FF} = 6.3V_{ac}$  (6)

## **APPLICATIONS**

DON'T CARE BUFFER STORES LEAST SIGNIFICANT CONTROL MEMORIES POST MORTEM MEMORIES (WEAPON SYSTEMS) ARTIFICIAL MEMORY SYSTEMS NON-INTELLIGENT MICRO CONTROLLERS FIRST-IN NEVER-OUT (FINO) ASYNCHRONOUS **BUFFERS**

OVERFLOW REGISTER (BIT BUCKET)

#### PROCESS TECHNOLOGY

The use of Signetics unique SEX(7) process yields Vth (var.) and allows the design(8) and production(9) of higher performance MOS circuits than can be obtained by competitor's techniques.

## FINAL SPECIFICATION (10)

#### BIPOLAR COMPATIBILITY

All data and clock inputs plus applicable outputs will interface directly or nearly directly with bipolar circuits of suitable characteristics. In any event use 1 amp fuses in all power supply and data lines.

#### INPUT PROTECTION

All terminals are provided with slip-on latex protectors for the prevention of Voltage Destruction. (PILL packaged devices do not require protection).

#### SILICON PACKAGING

Low cost silicon DIP packaging is implemented and reliability is assured by the use of a non-hermetic sealing technique which prevents the entrapment of harmful ions, but which allows the free exchange of friendly ions.

## SPECIAL FEATURES

Because of the employment of the Signetics' proprietary Sanderson-Rabbet Channel the 25120 will provide 50% higher speed than you will obtain.

#### COOLING

The 25120 is easily cooled by employment of a six-foot fan, 1/2" from the package. If the device fails, you have exceeded the ratings. In such cases, more air is recommended.

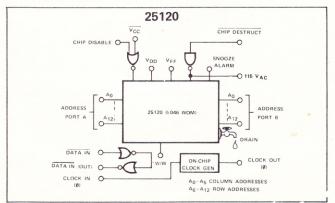

#### **BLOCK DIAGRAM**

## PART IDENTIFICATION

| TYPE  | "n" | TEMP. RANGE | PACKAGE             |

|-------|-----|-------------|---------------------|

| 25120 | 0   | 0 to -70°C  | Whatever's<br>Right |

- 7. You have a dirty mind. S.E.X. is Signetics EXtra Secret process. "One Shovel Full to One Shovel Full", patented by Yagura, Kashkooli, Converse and Al. Circa 1921.

- 8. J, Kane calls it design (we humor him).

- 9. See "Modern Production Techniques" by T. Arrieta (not yet written).

- 10. Final until we got a look at some actual parts.

- 11. Coffee breaks and lunch hours.

- 12. Due credit to alMAC for inspiration.

<sup>1. &</sup>quot;Neu" channel devices enhance or deplete regardless of gate polarity, either simultaneously or randomly. Sometimes not at all.

<sup>2. &</sup>quot;S.O.S." copyrighted U.S. Army Commissary, 1940.

<sup>3.</sup> Not applicable

You can somehow drive these inputs from TTL, the method

<sup>5.</sup> Measure at 1MHz, 25mVac, 1.9pF in series.

<sup>6.</sup> For the filaments, what else!

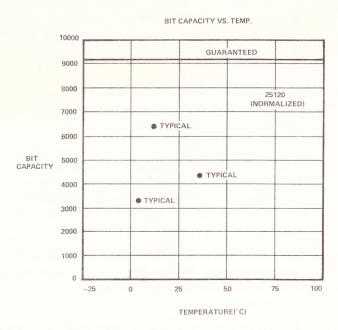

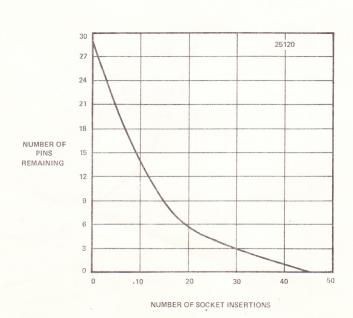

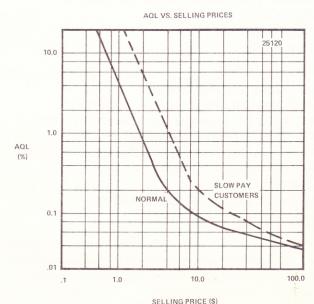

#### TYPICAL CHARACTERISTIC CURVES

# **Do Not Copy**